Diplomado en Inferencia en MCU/NPUs (TFLite/ONNX/TensorRT)

Sobre nuestro Diplomado en Inferencia en MCU/NPUs (TFLite/ONNX/TensorRT)

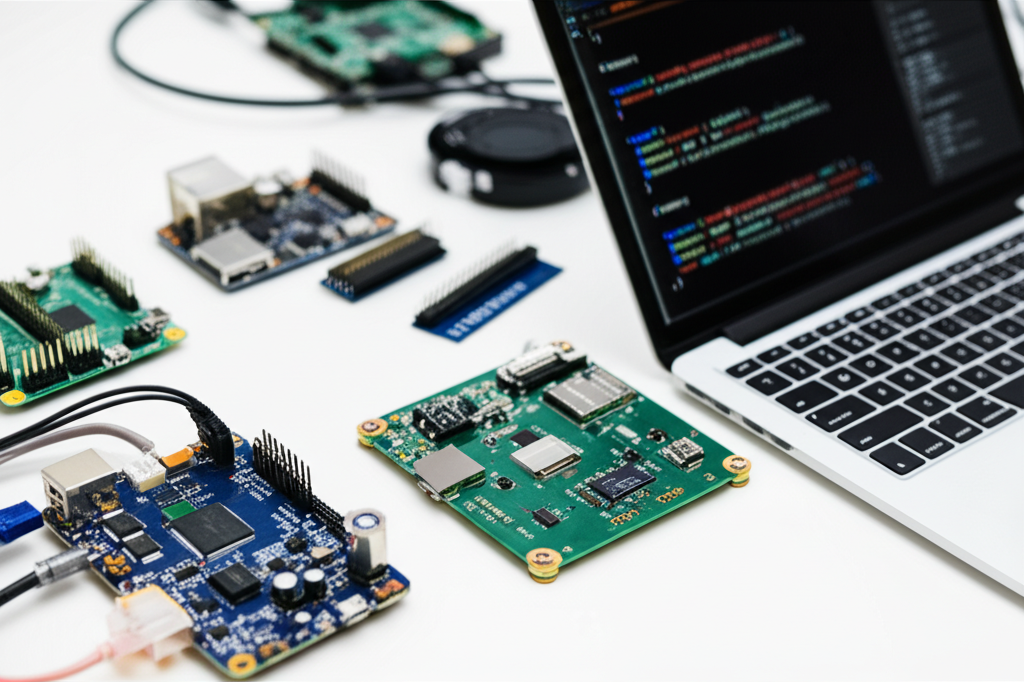

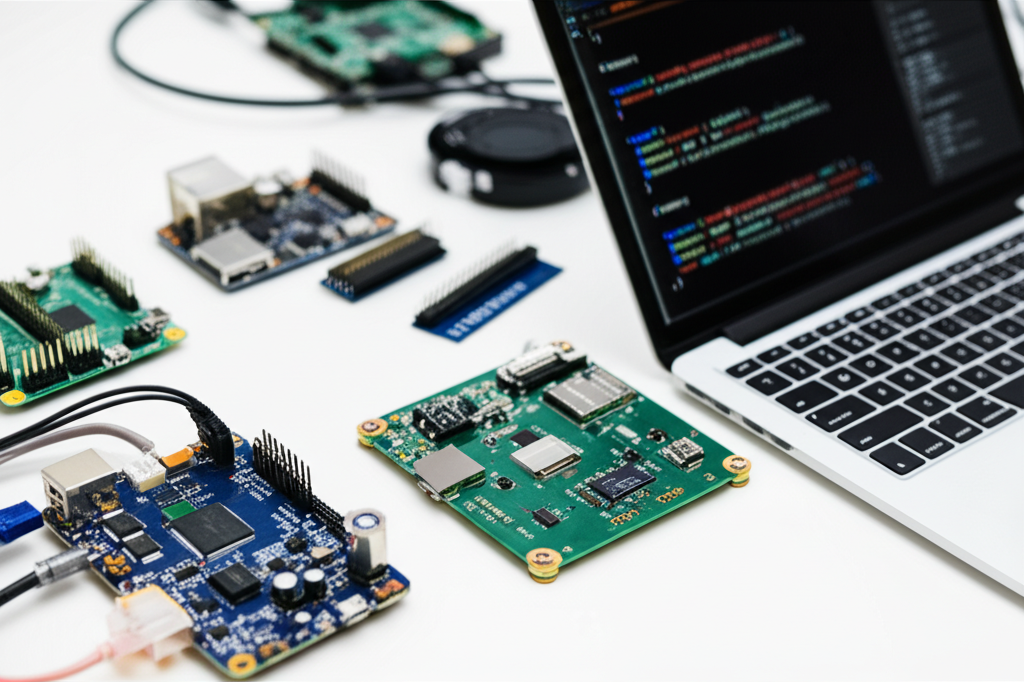

El Diplomado en Inferencia en MCU/NPUs (TFLite/ONNX/TensorRT) se centra en la optimización y despliegue de modelos de Machine Learning (ML) en dispositivos de bajo consumo como MCUs (Microcontroladores) y NPUs (Unidades de Procesamiento Neural). Se aborda el uso de frameworks como TFLite, ONNX y TensorRT para la conversión, cuantización y optimización de modelos, permitiendo la inferencia eficiente en el borde. Se profundiza en la aplicación de estos modelos en el campo de la Visión por Computadora, Procesamiento de Señales y otras áreas donde la inferencia en tiempo real y con bajo consumo son críticas, proporcionando una base sólida para el desarrollo de soluciones edge AI.

El programa ofrece experiencia práctica en la implementación de modelos optimizados, evaluación de rendimiento y benchmarking en diferentes arquitecturas de hardware. Se exploran casos de uso en domótica, robótica, y dispositivos IoT, desarrollando habilidades para la creación de soluciones eficientes y escalables. Se prepara para roles como ingenieros de ML embarcado, desarrolladores de edge AI y científicos de datos especializados en optimización de modelos.

Palabras clave objetivo (naturales en el texto): inferencia, MCU, NPU, TFLite, ONNX, TensorRT, Machine Learning, edge AI, optimización de modelos, visión por computadora, IoT.

Diplomado en Inferencia en MCU/NPUs (TFLite/ONNX/TensorRT)

- Modalidad: Online

- Duración: 8 meses

- Horas: 900 H

- Idioma: ES / EN

- Créditos: 60 ECTS

- Fecha de matrícula: 30-04-2026

- Fecha de inicio: 10-06-2026

- Plazas disponibles: 9

1.799 $

Competencias y resultados

Qué aprenderás

1. Optimización de Modelos de IA para MCU/NPU: TFLite, ONNX, TensorRT

- Comprender y aplicar técnicas avanzadas de optimización para modelos de Inteligencia Artificial (IA) diseñados para Microcontroladores (MCU) y Unidades de Procesamiento Neuronal (NPU).

- Dominar el uso de frameworks de optimización de IA, incluyendo TensorFlow Lite (TFLite), ONNX (Open Neural Network Exchange) y TensorRT.

- Aprender a cuantificar, podar y comprimir modelos de IA para reducir su tamaño y complejidad, optimizando su rendimiento en dispositivos con recursos limitados.

- Explorar estrategias de optimización específicas para diferentes arquitecturas de MCU/NPU, considerando las limitaciones de hardware y las necesidades de rendimiento.

- Implementar modelos de IA optimizados en dispositivos MCU/NPU, evaluando su rendimiento y eficiencia energética.

- Analizar las compensaciones entre precisión, tamaño del modelo y velocidad de inferencia.

- Utilizar herramientas y técnicas para el perfilado y la depuración de modelos de IA optimizados en entornos de MCU/NPU.

2. Despliegue Eficiente de Modelos de IA en MCU/NPU: TFLite, ONNX, TensorRT

- Comprender y aplicar la optimización de modelos de IA para MCU/NPU.

- Dominar el uso de TFLite para la inferencia de modelos en dispositivos embebidos.

- Aprovechar ONNX para la interoperabilidad y el despliegue de modelos.

- Utilizar TensorRT para la aceleración de la inferencia en hardware específico.

- Optimizar el rendimiento de los modelos en términos de velocidad, tamaño y consumo de energía.

- Implementar estrategias de cuantización y compresión de modelos.

- Explorar las arquitecturas de hardware MCU/NPU y sus capacidades.

- Desarrollar aplicaciones prácticas que utilicen modelos de IA en entornos embebidos.

3. Diseño y validación integral orientado al usuario (del modelado a la manufactura)

Aprenderás a integrar todo el proceso de desarrollo de producto desde la concepción del modelo hasta su validación final, aplicando metodologías centradas en el usuario. Desarrollarás competencias en diseño paramétrico, ergonomía, simulación, materiales sostenibles, visualización 3D y gestión de manufactura, garantizando soluciones eficientes, seguras y alineadas con los estándares industriales actuales.

4. Implementación Optimizada de IA en MCU/NPU: TFLite, ONNX, TensorRT

4. Implementación Optimizada de IA en MCU/NPU: TFLite, ONNX, TensorRT

- Dominar el proceso de optimización de modelos de IA para MCU/NPU.

- Comprender y aplicar las bibliotecas TFLite, ONNX y TensorRT para la inferencia en dispositivos de bajo consumo.

- Aprender técnicas de cuantización, pruning y otras optimizaciones para reducir el tamaño y la complejidad de los modelos.

- Implementar modelos de IA en diferentes arquitecturas de MCU/NPU, incluyendo la configuración de hardware y software.

- Evaluar el rendimiento de los modelos optimizados en términos de precisión, velocidad de inferencia y consumo de energía.

- Identificar y solucionar problemas comunes en la implementación de IA en dispositivos embebidos.

- Aplicar las optimizaciones aprendidas a casos prácticos de visión por computador, procesamiento de lenguaje natural y otras aplicaciones.

- Utilizar herramientas de perfilado y depuración para optimizar aún más el rendimiento de los modelos.

- Familiarizarse con las últimas tendencias en la optimización de IA para dispositivos embebidos.

- Desarrollar habilidades para la creación y el despliegue de soluciones de IA eficientes y de bajo consumo en el mundo real.

5. Inferencias de IA Optimizadas en MCU/NPU: TFLite, ONNX, TensorRT

- Introducción a la optimización de inferencia de IA en MCU/NPU.

- Fundamentos de TensorFlow Lite (TFLite): comprensión y uso.

- Implementación de modelos ONNX para inferencia optimizada.

- Aceleración de inferencia con TensorRT: optimización y despliegue.

- Estrategias para la selección de hardware: MCU vs. NPU.

- Técnicas de cuantización y compresión de modelos para optimización.

- Análisis de rendimiento: métricas y evaluación de la eficiencia.

- Desarrollo de aplicaciones prácticas: casos de estudio y ejemplos.

- Herramientas y bibliotecas para la optimización de inferencia.

- Tendencias futuras en la optimización de IA para dispositivos embebidos.

6. Aceleración de IA: Optimización y Despliegue en MCU/NPU (TFLite, ONNX, TensorRT)

Aprenderás a integrar todo el proceso de desarrollo de producto desde la concepción del modelo hasta su validación final, aplicando metodologías centradas en el usuario. Desarrollarás competencias en diseño paramétrico, ergonomía, simulación, materiales sostenibles, visualización 3D y gestión de manufactura, garantizando soluciones eficientes, seguras y alineadas con los estándares industriales actuales.

Para quien va dirigido nuestro:

Diplomado en Inferencia en MCU/NPUs (TFLite/ONNX/TensorRT)

- Ingenieros/as con título en Ingeniería Aeroespacial, Ingeniería Mecánica, Ingeniería Industrial, Ingeniería Automática o campos relacionados.

- Profesionales que trabajen en empresas OEM de aeronaves de ala rotatoria/eVTOL, MRO, firmas de consultoría o centros tecnológicos.

- Expertos/as en áreas de Pruebas de Vuelo (Flight Test), Certificación aeronáutica, Aviónica, Control de sistemas y Dinámica de vuelo que deseen profundizar sus conocimientos.

- Personal de organismos reguladores/autoridades y perfiles involucrados en proyectos de Movilidad Aérea Urbana (UAM)/eVTOL, que requieran conocimientos en cumplimiento normativo (compliance).

**Requisitos recomendados:** Se sugiere una sólida base en aerodinámica, control de sistemas y estructuras. Se requiere un nivel de idioma ES/EN B2+/C1. Se ofrecen cursos de nivelación (*bridging tracks*) para cubrir posibles deficiencias.

- Standards-driven curriculum: trabajarás con CS-27/CS-29, DO-160, DO-178C/DO-254, ARP4754A/ARP4761, ADS-33E-PRF desde el primer módulo.

- Laboratorios acreditables (EN ISO/IEC 17025) con banco de rotor, EMC/Lightning pre-compliance, HIL/SIL, vibraciones/acústica.

- TFM orientado a evidencia: safety case, test plan, compliance dossier y límites operativos.

- Mentorado por industria: docentes con trayectoria en rotorcraft, tiltrotor, eVTOL/UAM y flight test.

- Modalidad flexible (híbrido/online), cohortes internacionales y soporte de SEIUM Career Services.

- Ética y seguridad: enfoque safety-by-design, ciber-OT, DIH y cumplimiento como pilares.

1.1 Panorama Edge AI: inferencia vs entrenamiento, latencia, energía, coste y restricciones de memoria.

1.2 Arquitecturas objetivo: MCU (ARM Cortex-M, RISC-V), SoC edge, y NPUs/accelerators (conceptos y diferencias).

1.3 Tipos de cargas: visión, audio, sensores, series temporales; perfiles de cómputo y memoria.

1.4 Modelos y operaciones: convolución, depthwise, attention, activaciones; qué cuesta realmente en embedded.

1.5 Precisión numérica: FP32/FP16/BF16/INT8/INT4; impacto en tamaño, latencia y consumo.

1.6 Métricas clave: throughput, latency P50/P95, SRAM/Flash/VRAM, energía por inferencia, temperatura.

1.7 Toolchains y ecosistemas: TFLite/TFLM, ONNX Runtime, TensorRT; compatibilidades y límites.

1.8 Pipeline de despliegue: exportación, optimización, cuantización, compilación, benchmark y validación.

1.9 Buenas prácticas de reproducibilidad: seeds, versiones, artefactos, CI para modelos en edge.

1.10 Seguridad y confiabilidad: integridad del modelo, actualizaciones OTA, rollback y telemetría.

2.1 Eficiencia arquitectónica: MobileNet/EfficientNet/ShuffleNet/TinyML patterns.

2.2 Trade-offs: ancho vs profundidad, resolución vs precisión, multi-task vs single-task.

2.3 Operadores “hardware friendly”: conv2d, dwconv, 1×1, pooling; evitar ops costosas.

2.4 Memoria intermedia (activations): cómo domina el footprint en MCU.

2.5 Reutilización de buffers y planning de tensores: estrategias para SRAM limitada.

2.6 Preprocesado y postprocesado: coste, precisión, y dónde ejecutarlos (CPU vs acelerador).

2.7 Compresión estructural: pruning, low-rank, distillation; cuándo conviene en edge.

2.8 Diseño por caso de uso: wake-word, anomaly detection, clasificación visión, segmentación ligera.

2.9 Criterios de aceptación: precisión mínima, latencia máxima, consumo máximo, temperatura.

2.10 Checklist de “deployability”: validación previa a exportación (ops compatibles, rangos, cuantización).

3.1 TFLite vs TFLM: runtime, limitaciones, kernels y memoria.

3.2 Conversión TF → TFLite: SavedModel, Keras, firmas, entradas y salidas.

3.3 Operadores soportados: built-ins, select TF ops, y estrategias de reemplazo.

3.4 Cuantización TFLite: dynamic range, float16, full-integer INT8, INT16.

3.5 Calibración: representative dataset, rangos, sensibilidad por capa.

3.6 TFLM memory planner: arena, tensor allocation, buffers y profiling de SRAM.

3.7 Aceleración en MCU: CMSIS-NN, Ethos-U (conceptual), kernels optimizados y delegados.

3.8 Integración en firmware: build system, C/C++, loops de inferencia, interrupciones y RTOS.

3.9 Benchmarks en dispositivo: latencia, energía, temperatura; medición y registro.

3.10 Validación en campo: drift, robustez, tolerancias y estrategias de actualización.

4.1 ONNX como formato de intercambio: graph, opsets, tensores, initializers.

4.2 Exportación desde PyTorch/TF: buenas prácticas, control de opset y formas dinámicas.

4.3 Simplificación de gráficos: onnx-simplifier, folding de constantes, eliminación de nodos.

4.4 Validación numérica: parity checks, tolerancias, pruebas por lote y por capa.

4.5 Problemas típicos: ops no soportadas, shapes, broadcast, dynamic axes.

4.6 Cuantización ONNX: QDQ vs QOperator, calibración y compatibilidad con runtimes.

4.7 ONNX Runtime: CPU, NNAPI, CoreML, CUDA; cuándo usar cada backend.

4.8 Perfilado y tracing: identificar cuellos de botella por operador y por memoria.

4.9 Interoperabilidad: ONNX ↔ TFLite, límites reales y estrategias de mantenimiento.

4.10 Versionado del modelo: opset, runtime, hardware target; control de cambios.

5.1 Conceptos TensorRT: engine, builder, network definition, optimization profiles.

5.2 Precision modes: FP16, INT8, calibración y sensibilidad por capa.

5.3 Importación de ONNX a TensorRT: parsing, errores comunes y soluciones.

5.4 Plugins y layers custom: cuándo son necesarios y riesgos de mantenimiento.

5.5 Tácticas de optimización: fusion, tactic selection, workspace, sparse weights.

5.6 Batch, dynamic shapes y perfiles: impacto en latencia y memoria.

5.7 Deployment: serialización de engine, compatibilidad por versión, caching y warmup.

5.8 Integración con pipelines: DeepStream, GStreamer, CUDA streams (visión general).

5.9 Benchmarking: trtexec, Nsight (conceptual), métricas y reproducibilidad.

5.10 Operación en producción: monitoreo, fallback, actualizaciones y rollback.

6.1 Fundamentos cuantización: escala, zero-point, simétrica/asimétrica, per-tensor/per-channel.

6.2 INT8 end-to-end: requisitos y trampas en TFLite/ONNX/TensorRT.

6.3 Calibración de datos: representatividad, sesgos, selección de muestras.

6.4 Post-training quantization vs QAT: cuándo usar cada una.

6.5 Sensibilidad por capa: detección, mitigación, “keep FP16/FP32” selectivo.

6.6 Range clipping, bias correction y smooth quant: estrategias prácticas.

6.7 Cuantización de activaciones vs pesos: impacto en precisión y latencia.

6.8 Evaluación de precisión: top-k, mAP, IoU, métricas por clase y robustez.

6.9 Validación en dominio: datasets reales, ruido, condiciones ambientales y drift.

6.10 Criterios de aceptación: definir umbrales de precisión por caso de uso y riesgo.

7.1 Perfilado sistemático: hipótesis, medición, control de variables.

7.2 Análisis de latencia: kernels, pre/post, I/O, copias de memoria y sincronizaciones.

7.3 Memoria: activations, weights, buffers; técnicas para reducir footprint.

7.4 Scheduling y pipelines: batching, pipelining, doble buffer, concurrencia.

7.5 Energía: medición, métricas (mJ/inferencia), estrategias de reducción.

7.6 Thermal throttling: causas, detección y mitigación.

7.7 Optimización del preprocesado: SIMD, lookup tables, fixed-point.

7.8 Compilación y flags: -O2/-O3, LTO, CMSIS-DSP/NN, NEON (visión general).

7.9 Robustez y fallbacks: degradación controlada (resolución, FPS, precisión).

7.10 Reporte de optimización: documentación para repetibilidad y auditoría.

8.1 Arquitectura de software: módulos, drivers, RTOS, colas, prioridades y watchdogs.

8.2 Ciclo de inferencia: adquisición → preprocesado → inferencia → postprocesado → acción.

8.3 Gestión de modelos: almacenamiento, integridad, firma, cifrado, control de versión.

8.4 OTA para modelos: estrategias, delta updates, rollback y compatibilidad.

8.5 Telemetría: latencia, errores, drift, métricas de confianza; privacidad.

8.6 Testing: unit tests de pre/post, regression de precisión, pruebas en hardware-in-the-loop.

8.7 Observabilidad: logs, métricas y trazas; diagnóstico de fallos en campo.

8.8 Gestión de datasets: recolección, etiquetado, y realimentación desde producción.

8.9 Cumplimiento: seguridad, privacidad, documentación y trazabilidad.

8.10 Entrega continua: pipeline CI/CD para artefactos (TFLite/ONNX/engine) y firmware.

9.1 Visión: clasificación ligera con restricciones de FPS y memoria.

9.2 Detección: modelos compactos, NMS, postprocesado eficiente.

9.3 Audio: wake-word y clasificación acústica; MFCC y fixed-point.

9.4 Sensores: series temporales para anomalías en vibración/temperatura.

9.5 Optimización por plataforma: MCU vs NPU vs GPU edge; criterios de elección.

9.6 Comparación TFLite vs ONNX Runtime vs TensorRT: tiempos, precisión y mantenimiento.

9.7 Robustez: ruido, iluminación, variaciones; pruebas de estrés.

9.8 Seguridad funcional: umbrales, incertidumbre, y acciones seguras.

9.9 Evaluación final: benchmark integral (latencia, energía, memoria, precisión).

9.10 Documentación del laboratorio: reporte técnico reproducible y checklist de despliegue.

10.1 Definición del caso: requisitos de precisión, latencia, energía y memoria.

10.2 Selección de modelo base y estrategia de eficiencia.

10.3 Exportación a TFLite/ONNX según objetivo; control de compatibilidad de ops.

10.4 Cuantización (PTQ/QAT) y calibración con dataset representativo.

10.5 Compilación/engine: TensorRT (si aplica) y verificación de parity.

10.6 Integración: loop de inferencia, pre/post, optimización de I/O.

10.7 Benchmark en objetivo: medición de latencia, memoria y energía.

10.8 Validación en condiciones reales: robustez, drift y tolerancias.

10.9 Plan de despliegue: versionado, OTA, monitoreo y rollback.

10.10 Entrega final: informe completo, artefactos, checklist y plan de mantenimiento.

- Metodología hands-on: test-before-you-trust, design reviews, failure analysis, compliance evidence.

- Software (según licencias/partners): MATLAB/Simulink, Python (NumPy/SciPy), OpenVSP, SU2/OpenFOAM, Nastran/Abaqus, AMESim/Modelica, herramientas de acústica, toolchains de planificación DO-178C.

- Laboratorios SEIUM: banco de rotor a escala, vibraciones/acústica, EMC/Lightning pre-compliance, HIL/SIL para AFCS, adquisición de datos con strain gauging.

- Estándares y cumplimiento: EN 9100, 17025, ISO 27001, GDPR.

Proyectos tipo capstones

- Optimización IA MCU/NPU: Modelos IA optimizados (TFLite/ONNX/TensorRT); Despliegue y ejecución eficiente.

- Compresión IA: Modelos IA comprimidos y ejecutados en dispositivos de baja potencia.

- Implementación y Aceleración IA: IA optimizada e implementada en MCU/NPU; inferencias optimizadas.

- Optimización IA MCU/NPU: Modelos IA optimizados (TFLite/ONNX/TensorRT); Despliegue y ejecución eficiente.

- Compresión IA: Modelos IA comprimidos y ejecutados en dispositivos de baja potencia.

- Implementación y Aceleración IA: IA optimizada e implementada en MCU/NPU; inferencias optimizadas.

- IA Embarcada para Navegación: Optimización y despliegue de modelos IA (TFLite, ONNX, TensorRT) en MCU/NPU para detección de obstáculos, navegación autónoma y reconocimiento de señales marítimas.

- Optimización IA MCU/NPU: Modelos TFLite, ONNX, TensorRT; compresión; inferencia eficiente.

- Despliegue y Aceleración IA: Diseño optimizado para dispositivos de baja potencia.

- Implementación IA: Estrategias para inferencias rápidas y optimizadas.

- IA embarcada: Optimización, despliegue e inferencia eficiente en MCU/NPU (TFLite, ONNX, TensorRT).

- Compresión de modelos: Reducción de tamaño para dispositivos de baja potencia.

- Aceleración IA: Implementación optimizada de IA.

- Evaluación de rendimiento: Benchmarking y análisis comparativo.

Admisiones, tasas y becas

- Perfil: Formación en Ingeniería Informática, Matemáticas, Estadística o campos relacionados; experiencia práctica en NLP y sistemas de recuperación de información valorada.

- Documentación: CV actualizado, expediente académico, SOP/ensayo de propósito, ejemplos de proyectos o código (opcional).

- Proceso: solicitud → evaluación técnica de perfil y experiencia → entrevista técnica → revisión de casos prácticos → decisión final → matrícula.

- Tasas:

- Pago único: 10% de descuento.

- Pago en 3 plazos: sin comisiones; 30% a la inscripción + 2 pagos mensuales iguales del 35% restante.

- Pago mensual: disponible con comisión del 7% sobre el total; revisión anual.

- Becas: por mérito académico, situación económica y fomento de la inclusión; convenios con empresas del sector para becas parciales o totales.

Consulta “Calendario & convocatorias”, “Becas & ayudas” y “Tasas & financiación” en el mega-menú de SEIUM

¿Tienes dudas?

Nuestro equipo está listo para ayudarte. Contáctanos y te responderemos lo antes posible.